Icarus VerilogでVerilogシミュレートしてみた

お久しぶりです。やぎ湯です。

これからFPGAもいじっていくつもりでいるので、今回はVerilog-HDLについて学ぼうと、Icarus Verilogでコンパイルと波形のシミュレートをやってみました。

OSはOSXでやりました。

まず、autoconf、iverilog、GTKwaveのインストールからです。ターミナルから、

$ mkdir aconf

$ cd aconf

$ curl -OL http://ftpmirror.gnu.org/autoconf/autoconf-2.68.tar.gz

$ tar xvzf autoconf-2.68.tar.gz

$ cd autoconf-2.68

$ ./configure

$ make

$ sudo make install

でautoconfをインストールします。

次に

$ git clone git://github.com/steveicarus/iverilog.git

を実行してiverilogを入手し、

$ cd iverilog

$ autoconf

$ ./configure

$ make

でiverilogをコンパイルします。動作確認のために、

$ make check

を実行して、最後の行に"Hello, World"と出ていればOKです。

そして、

$ sudo make install

でインストールします。

GTKwaveは、このリンク先の

http://gtkwave.sourceforge.net

下の画像の矢印のところからダウンロードしてアプリとして入手しました。

あとはターミナルから、

$ iverilog -o [出力ファイル名] [Verilogソースファイル]

という感じに書いてやればVerilogソースコードのコンパイルができる、というわけです。

例えば、

$ ls iverilog/examples/

で見つかるhello.vlなら、

$ iverilog -o hello ./iverilog/examples/hello.vl

$ ./hello

で実行でき、"Hello, World"と実行されます。

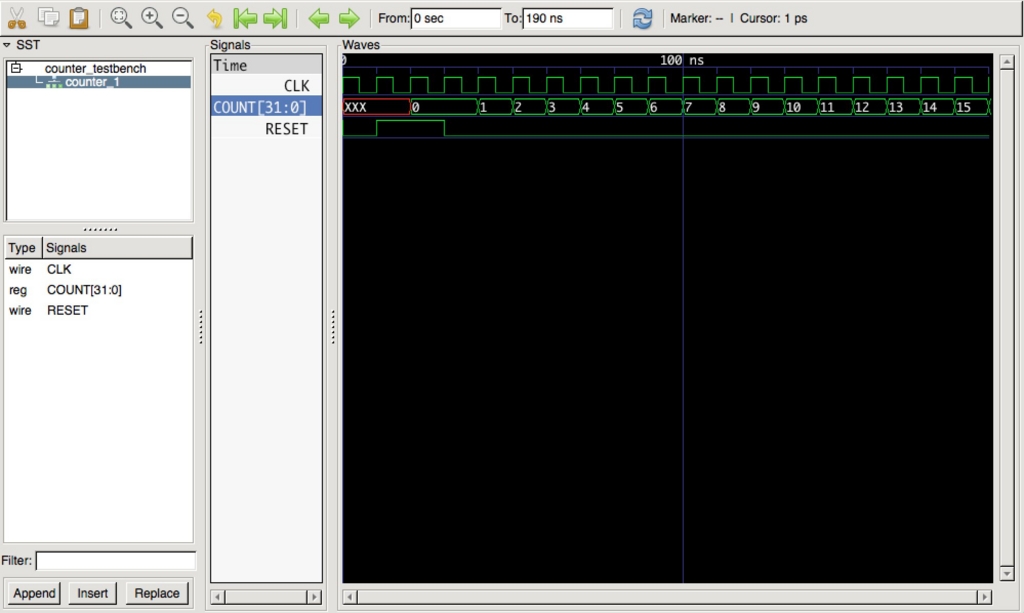

こんなふうにして、レジスタをカウントアップする回路をVerilogで記述し、コンパイル・シミュレーションし、wave.vcd(波形データファイル)を生成しました。

※ソースコードはこちらより↓

http://cellspe.matrix.jp/zerofpga/icarus.html

リンク先のページのように操作していき、wave.vcdを波形として出力しました。

これでFPGAボードが届くまでVerilogの記述の練習ができそうです。まだMacにParallelsでWindowsを入れてなく、WindowsPCがデスクトップだけなのでVerilogをいじる環境が外出先になかったわけです(笑) その点でもIcarus Verilogは便利だと思いましたね。これからFPGAの勉強も頑張っていきたいと思います。

それでは次の更新まで。

投げ銭していただければ、めちゃくちゃ喜ぶのでよかったらよろしくお願いします。